物理層信號完整性測試(SI/PI)UFS信號完整性測試多端口矩陣測試

UFS 信號完整性之阻抗匹配關(guān)鍵

阻抗匹配在 UFS 信號完整性里占據(jù)重心地位。傳輸線的阻抗若與 UFS 設(shè)備、連接線纜等不匹配,信號傳輸時(shí)就會(huì)出現(xiàn)反射現(xiàn)象。這就如同聲音在空蕩蕩的大房間里產(chǎn)生回聲,反射的信號會(huì)干擾原始信號,致使信號失真、衰減,嚴(yán)重影響數(shù)據(jù)傳輸質(zhì)量。以 UFS 的差分信號對為例,理想狀態(tài)下,需將其阻抗精細(xì)控制在 100Ω 。實(shí)際設(shè)計(jì)時(shí),要綜合考量 PCB 板材特性、走線寬度、線間距等因素,利用專業(yè)工具進(jìn)行仿真,優(yōu)化布線策略,盡可能讓傳輸線阻抗與目標(biāo)值契合。只有實(shí)現(xiàn)良好的阻抗匹配,才能減少信號反射,保障 UFS 信號穩(wěn)定傳輸,為數(shù)據(jù)準(zhǔn)確讀寫筑牢根基 UFS 信號完整性測試之線路布局優(yōu)化?物理層信號完整性測試(SI/PI)UFS信號完整性測試多端口矩陣測試

UFS 信號完整性測試之虛擬現(xiàn)實(shí)場景需求

虛擬現(xiàn)實(shí)(VR)場景對數(shù)據(jù)處理和存儲(chǔ)要求苛刻,UFS 信號完整性測試要滿足其特殊需求。VR 設(shè)備運(yùn)行時(shí),需實(shí)時(shí)讀取大量 3D 模型、紋理等數(shù)據(jù),UFS 信號不穩(wěn)定會(huì)導(dǎo)致畫面卡頓、延遲,嚴(yán)重影響用戶體驗(yàn)。測試時(shí),模擬 VR 場景下的大數(shù)據(jù)量、高頻率讀寫操作。優(yōu)化 UFS 硬件設(shè)計(jì),如提升存儲(chǔ)帶寬、采用高速緩存技術(shù),配合針對性信號完整性測試,確保 UFS 能快速、準(zhǔn)確傳輸數(shù)據(jù)。穩(wěn)定的信號完整性為 VR 場景提供流暢數(shù)據(jù)支持,助力用戶沉浸在高質(zhì)量虛擬現(xiàn)實(shí)體驗(yàn)中。 測量UFS信號完整性測試一致性測試UFS 硬件架構(gòu)與信號完整性關(guān)聯(lián)?

UFS 信號完整性之噪聲干擾剖析

噪聲干擾嚴(yán)重威脅 UFS 信號完整性。在 UFS 系統(tǒng)所處的復(fù)雜電磁環(huán)境里,存在多種噪聲源。外部的,如附近的無線通信設(shè)備、電機(jī)等產(chǎn)生的電磁輻射,會(huì)耦合進(jìn) UFS 傳輸線路;內(nèi)部的,像芯片內(nèi)部電路開關(guān)動(dòng)作、電源紋波等,也會(huì)帶來噪聲。這些噪聲疊加在正常信號上,致使信號波形畸變,增加誤碼率。例如,電源噪聲會(huì)使信號電平出現(xiàn)波動(dòng),影響數(shù)據(jù)的正確識別。為應(yīng)對噪聲干擾,可采用屏蔽措施,如在 PCB 板上布置接地屏蔽過孔,隔離外界電磁干擾;優(yōu)化電源設(shè)計(jì),降低電源紋波,減少內(nèi)部噪聲產(chǎn)生。只有有效抑制噪聲,才能確保 UFS 信號 “純凈”,實(shí)現(xiàn)穩(wěn)定的數(shù)據(jù)傳輸

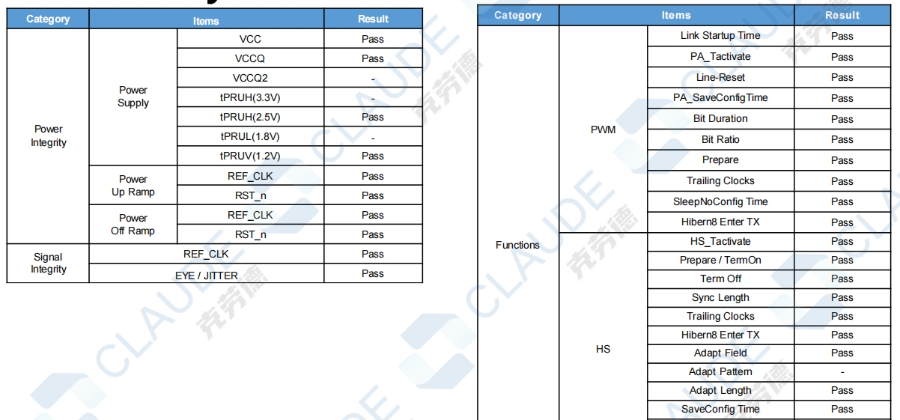

UFS 信號完整性測試之測試流程概述

UFS 信號完整性測試有嚴(yán)謹(jǐn)流程。首先搭建測試環(huán)境,連接好 UFS 設(shè)備、測試儀器等。接著對發(fā)射端進(jìn)行測試,測量信號電壓、時(shí)間等參數(shù)。然后測試接收端,評估靈敏度與誤碼率。過程中,利用 TDR 測阻抗,用示波器觀察眼圖、抖動(dòng)等。測試完成后,分析數(shù)據(jù),判斷信號完整性是否達(dá)標(biāo)。若不達(dá)標(biāo),排查問題并整改,重新測試,確保 UFS 信號滿足性能要求。

UFS 信號完整性測試之環(huán)境因素考量

測試 UFS 信號完整性時(shí),環(huán)境因素不可忽視。溫度變化可能影響電子元件性能,導(dǎo)致信號參數(shù)改變。濕度太高,線路可能受潮,引發(fā)短路等問題,影響信號傳輸。電磁環(huán)境復(fù)雜,外界電磁干擾會(huì)使信號失真。所以,測試需在穩(wěn)定溫濕度環(huán)境中進(jìn)行,同時(shí)做好電磁屏蔽,減少環(huán)境因素對 UFS 信號完整性測試結(jié)果的干擾,保證測試準(zhǔn)確性。 UFS 信號完整性測試之新興測試技術(shù)應(yīng)用?

UFS 信號完整性測試之信號質(zhì)量評估參數(shù)

UFS 信號完整性測試依據(jù)多項(xiàng)信號質(zhì)量評估參數(shù)。上升時(shí)間、下降時(shí)間反映信號變化快慢,過快或過慢都可能引發(fā)問題。信號噪聲影響信號清晰度,噪聲過大易使信號誤判。通過測量這些參數(shù),能評估信號質(zhì)量。例如,上升時(shí)間過長,信號沿變緩,可能導(dǎo)致數(shù)據(jù)傳輸速率下降。依據(jù)評估參數(shù),可針對性優(yōu)化信號傳輸,滿足 UFS 信號完整性要求。

UFS 信號完整性測試之物理層協(xié)議影響

UFS 使用 MIPI M-PHY 作為物理層協(xié)議,對信號完整性影響明顯。該協(xié)議支持高速差分信號傳輸,提高數(shù)據(jù)速率。但隨著速率提升,信號完整性挑戰(zhàn)增大。在測試中,要關(guān)注物理層協(xié)議規(guī)定的電氣特性、信號擺幅等。例如,減少信號擺幅雖能降低功耗,卻可能影響信噪比。遵循物理層協(xié)議規(guī)范,優(yōu)化信號傳輸,是保障 UFS 信號完整性的基礎(chǔ)。 UFS 信號完整性測試之長期穩(wěn)定性測試?解決方案UFS信號完整性測試測試工具

UFS 信號完整性測試之信號完整性與功耗關(guān)系?物理層信號完整性測試(SI/PI)UFS信號完整性測試多端口矩陣測試

UFS 信號完整性與數(shù)據(jù)準(zhǔn)確性

UFS 信號完整性直接關(guān)系到數(shù)據(jù)準(zhǔn)確性。信號在傳輸中若發(fā)生反射、串?dāng)_、失真等問題,數(shù)據(jù)就可能出錯(cuò)。當(dāng)信號完整性良好,數(shù)據(jù)能準(zhǔn)確無誤地從發(fā)射端傳至接收端。比如在存儲(chǔ)設(shè)備讀取數(shù)據(jù)時(shí),穩(wěn)定的信號確保讀取數(shù)據(jù)與原始存儲(chǔ)數(shù)據(jù)一致。所以,保證 UFS 信號完整性,是實(shí)現(xiàn)數(shù)據(jù)準(zhǔn)確傳輸與存儲(chǔ)的重心,對設(shè)備數(shù)據(jù)處理可靠性意義重大。

UFS 信號完整性測試之阻抗控制

阻抗控制是 UFS 信號完整性測試重點(diǎn)。傳輸線阻抗需匹配,否則信號反射嚴(yán)重,降低信號質(zhì)量。通過 TDR(時(shí)域反射計(jì))測量傳輸線阻抗,要求為 50Ω±5% 。若阻抗突變,會(huì)導(dǎo)致信號畸變,影響數(shù)據(jù)傳輸。在布線時(shí),精心設(shè)計(jì)線路長度、寬度等,確保阻抗穩(wěn)定。良好的阻抗控制能減少信號損耗,是 UFS 信號完整性測試與保障信號高效傳輸?shù)年P(guān)鍵環(huán)節(jié)。 物理層信號完整性測試(SI/PI)UFS信號完整性測試多端口矩陣測試

- 重慶DDR4測試系列 2025-12-15

- 江蘇眼圖測試以太網(wǎng)1000M物理層測試 2025-12-15

- 廣東眼圖測試PCIE3.0TX一致性測試信號完整性測試 2025-12-15

- 四川自動(dòng)化DDR3測試 2025-12-15

- 自動(dòng)化PCIE3.0TX一致性測試聯(lián)系人 2025-12-15

- 儀器儀表測試UFS信號完整性測試快速出具檢測報(bào)告 2025-12-15

- 多端口矩陣測試以太網(wǎng)測試 2025-12-15

- 海南MIPI測試多端口矩陣測試 2025-12-15

- 貴州以太網(wǎng)測試產(chǎn)品介紹 2025-12-15

- 夾具測試UFS信號完整性測試信號完整性測試 2025-12-15

- 紹興車速傳感器直銷價(jià)格 2025-12-16

- 新疆可編程控制搖床廠家 2025-12-16

- 金山區(qū)質(zhì)量傳感器圖片 2025-12-16

- 北京晶圓接觸角測量儀報(bào)價(jià) 2025-12-16

- 天津磁電式編碼器 2025-12-16

- 階梯水價(jià)水表品牌 2025-12-16

- 黑龍江PC 機(jī)網(wǎng)絡(luò)控制充磁系統(tǒng) 2025-12-16

- 南通本地氣體檢測傳感器安裝 2025-12-16

- 陜西品牌皮托管市場價(jià) 2025-12-16

- 浙江手持式管道焊縫光譜儀 2025-12-16