夾具測試UFS信號完整性測試檢測

UFS 信號完整性之測試方法基礎

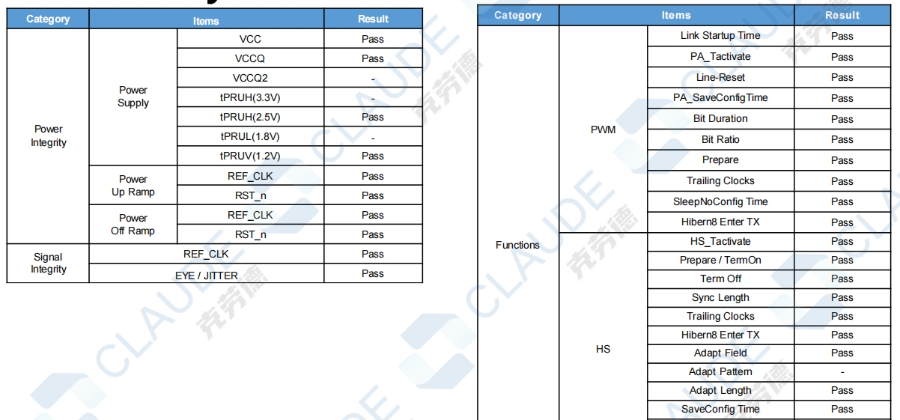

UFS 信號完整性測試是確保其性能的關鍵環(huán)節(jié)。常用測試方法包括使用示波器進行眼圖測試,通過觀察眼圖的眼高、眼寬等參數(shù),評估信號質量和噪聲容限。抖動測試則借助專業(yè)儀器,測量信號的隨機抖動(RJ)和周期抖動(PJ),確定總抖動(TJ)是否符合標準。此外,還可通過網絡分析儀測試傳輸線的 S 參數(shù),分析信號傳輸過程中的反射、損耗等情況。在測試時,要嚴格按照 UFS 標準設置測試條件,如不同速率下的信號參數(shù)要求。通過***、準確的測試,能及時發(fā)現(xiàn) UFS 信號完整性問題,為優(yōu)化設計提供依據。 UFS 信號完整性測試之不同應用場景測試差異?夾具測試UFS信號完整性測試檢測

UFS 信號完整性測試之信號完整性與未來發(fā)展趨勢

UFS 信號完整性測試對 UFS 未來發(fā)展至關重要。未來,UFS 將向更高速率、更低功耗發(fā)展,信號完整性挑戰(zhàn)更大。通過持續(xù)優(yōu)化測試方法,提前發(fā)現(xiàn)信號問題,能為 UFS 技術升級提供支持。例如,研發(fā)更先進測試設備,精細測量高速信號參數(shù)。重視信號完整性測試,是 UFS 順應未來發(fā)展趨勢,滿足市場對高性能存儲需求的必要條件。

UFS 信號完整性測試之信號完整性與產品創(chuàng)新

UFS 信號完整性測試助力產品創(chuàng)新。在研發(fā)新產品時,通過測試發(fā)現(xiàn)信號問題,促使工程師創(chuàng)新設計。如采用新線路布局、電路結構,解決信號完整性難題。良好的信號完整性為產品功能創(chuàng)新提供基礎,讓 UFS 設備實現(xiàn)更復雜應用。重視信號完整性測試,激發(fā)產品創(chuàng)新活力,推動 UFS 產品不斷升級。 解決方案UFS信號完整性測試接口測試UFS 信號完整性測試之環(huán)境因素考量?

UFS 硬件架構與信號完整性關聯(lián)

UFS 硬件架構設計影響信號完整性。差分對下方要保留連續(xù)地平面,防止跨分割,避免信號反射。接收端添加 100Ω 差分端接電阻(集成于主控或外置),能匹配阻抗,減少信號失真。相鄰信號對間距≥3 倍線寬,并用地屏蔽過孔(Guard Via),可抑制串擾。合理規(guī)劃硬件架構,為信號完整性提供物理基礎,確保 UFS 數(shù)據高速、準確傳輸,讓設備發(fā)揮比較好性能。

UFS 信號完整性測試之信號質量優(yōu)

化優(yōu)化 UFS 信號質量是信號完整性測試的目的之一。優(yōu)化信號上升 / 下降時間,能讓信號更清晰,減少碼間干擾。借助信號完整性分析工具,如 Ansys HFSS 進行仿真,可提前優(yōu)化布線策略。在設計階段,注重阻抗控制,保證傳輸線阻抗匹配,減少信號反射。良好的信號質量是 UFS 數(shù)據可靠傳輸?shù)谋U希芴嵘O備存儲與讀取數(shù)據的效率。

UFS信號完整性測試的重要性UFS(通用閃存存儲)作為高速存儲接口,其信號完整性直接影響數(shù)據傳輸?shù)姆€(wěn)定性和可靠性。隨著UFS3.1/4.0速率提升至23.2Gbps,微小的信號失真即可導致嚴重的誤碼問題。信號完整性測試能確保關鍵參數(shù)(如眼圖、抖動、阻抗匹配)符合JEDEC和MIPI標準,避免因信號劣化引發(fā)系統(tǒng)故障或數(shù)據錯誤。在研發(fā)階段,SI測試可快速定位設計缺陷(如走線過長、阻抗失配),優(yōu)化PCB布局,降低后期改版風險。量產階段則通過統(tǒng)計測試確保生產一致性,提升產品良率。此外,嚴苛環(huán)境測試(如高溫、振動)能驗證產品的長期可靠性。隨著5G、AI等應用對存儲性能要求不斷提高,完善的UFS信號完整性測試已成為保證產品競爭力、降低售后風險的必要手段。通過專業(yè)測試可提升產品穩(wěn)定性和市場接受度,避免因信號問題導致的高昂召回成本。

UFS 信號完整性測試之自動化測試優(yōu)勢?

UFS 信號完整性測試之維修中的信號檢測

設備維修時,UFS 信號完整性檢測可快速定位故障。若設備頻繁死機,可檢測 UFS 信號是否存在反射、串擾。用簡易示波器測量信號波形,與正常波形比對。若信號失真嚴重,可能是接口氧化、線路損壞等。通過信號檢測,能縮小故障范圍,提高維修效率,減少盲目更換元件的成本,讓設備盡快恢復正常運行。

UFS 信號完整性測試之芯片級測試與板級測試區(qū)別

UFS 芯片級測試與板級測試有明顯區(qū)別。芯片級測試在芯片出廠前進行,關注芯片內部信號傳輸,需高精度探針臺配合。板級測試針對 PCB 板上的 UFS 模塊,側重線路、接口對信號的影響。芯片級測試確保芯片本身性能,板級測試評估系統(tǒng)集成后的信號質量。二者相輔相成,共同保障 UFS 從芯片到整機的信號完整性。 UFS 信號完整性測試之信號完整性與抗振動性能?夾具測試UFS信號完整性測試檢測

UFS 信號完整性與傳輸線損耗?夾具測試UFS信號完整性測試檢測

UFS信號完整性基礎概念UFS信號完整性測試是驗證高速串行接口性能的關鍵環(huán)節(jié),主要評估信號在傳輸過程中的質量衰減。測試頻率覆蓋1.5GHz至11.6GHz(UFS3.1標準),重點關注差分信號的幅度、時序和噪聲特性。典型測試參數(shù)包括眼圖高度/寬度、抖動、插入損耗等,需滿足JEDECJESD220C規(guī)范要求。MIPIM-PHY物理層測試UFS采用MIPIM-PHY作為物理層接口,測試需關注HS-Gear3/4模式下的信號特性。關鍵指標:差分幅度200-400mVpp,共模電壓0.9-1.2V,上升時間<35ps。測試需使用16GHz以上帶寬示波器,通過TDR驗證阻抗匹配(100Ω±10%)。UniPro協(xié)議層驗證除物理層外,還需驗證UniPro協(xié)議層的信號完整性。測試內容包括:鏈路訓練過程信號穩(wěn)定性、LCC(Lane-to-LaneCalibration)后的時序一致性、電源狀態(tài)切換時的信號恢復時間。建議采用協(xié)議分析儀捕獲L1-L4狀態(tài)轉換波形。眼圖測試方法論UFS眼圖測試需累積≥1E6比特數(shù)據,評估標準:垂直開口≥70mV,水平開口≥0.6UI。需區(qū)分隨機抖動(RJ)和確定性抖動(DJ),其中RJ應<1.5psRMS。測試時建議關閉均衡功能以評估原始信號質量。夾具測試UFS信號完整性測試檢測

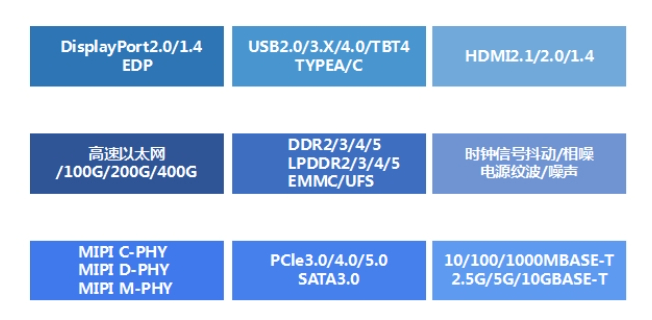

- HDMI測試DDR4測試DDR測試 2025-12-16

- 自動化UFS信號完整性測試方案商 2025-12-16

- 中國香港以太網測試工廠直銷 2025-12-16

- 信號完整性測試以太網測試安裝 2025-12-16

- 廣西信息化DDR4測試 2025-12-16

- 吉林DDR5測試參考價格 2025-12-16

- 重慶DDR4測試系列 2025-12-15

- 江蘇眼圖測試以太網1000M物理層測試 2025-12-15

- 廣東眼圖測試PCIE3.0TX一致性測試信號完整性測試 2025-12-15

- 四川自動化DDR3測試 2025-12-15

- 西藏醫(yī)用高溫無氧烘箱售后 2025-12-16

- 遼寧閃存熱流儀廠家 2025-12-16

- 靜安區(qū)質量極芯標控儀-S-10S用途 2025-12-16

- 廈門多點位移計現(xiàn)貨供應 2025-12-16

- 奧林巴斯手持式地質錄井勘探含量光譜儀 2025-12-16

- 海南ASM拉線位移傳感器 2025-12-16

- 徐匯區(qū)常用儀器儀表銷售哪里買 2025-12-16

- 全自動數(shù)顯洛氏硬度計經銷商 2025-12-16

- 黑龍江化妝品蒸汽質量檢測儀品牌推薦 2025-12-16

- 波長校準漫反射板哪家好 2025-12-16