西藏基于多芯MT-FA的三維光子互連系統(tǒng)

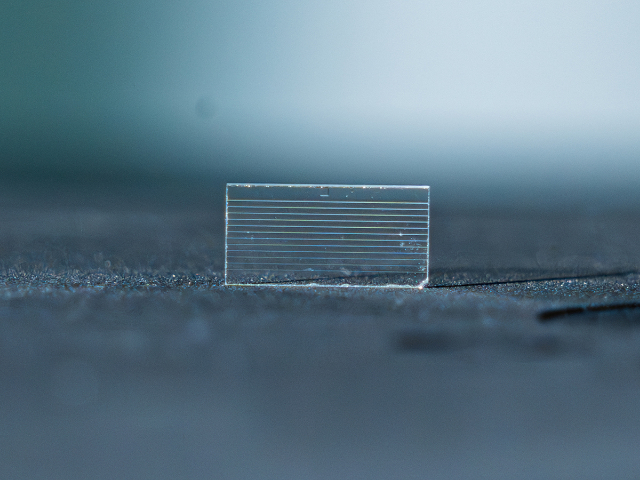

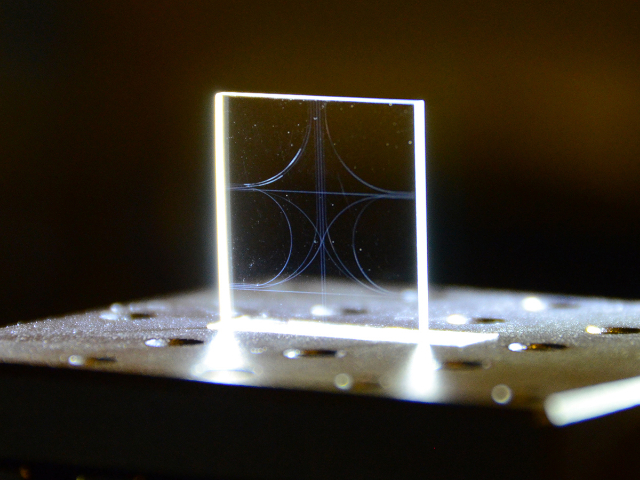

三維光子芯片的集成化發(fā)展對光連接器提出了前所未有的技術(shù)挑戰(zhàn),而多芯MT-FA光連接器憑借其高密度、低損耗、高可靠性的特性,成為突破這一瓶頸的重要組件。該連接器通過精密研磨工藝將多根光纖陣列集成于微米級插芯中,其42.5°端面全反射設(shè)計可實現(xiàn)光信號的90°轉(zhuǎn)向傳輸,配合低損耗MT插芯與亞微米級V槽定位技術(shù),使單通道插損控制在0.2dB以下,回波損耗優(yōu)于-55dB。在三維光子芯片的層間互連場景中,多芯MT-FA通過垂直堆疊架構(gòu)支持12至36通道并行傳輸,通道間距可壓縮至250μm,較傳統(tǒng)單芯連接器密度提升10倍以上。這種設(shè)計不僅滿足了光子芯片對空間緊湊性的嚴苛要求,更通過多通道同步傳輸將系統(tǒng)帶寬提升至Tbps級,為高算力場景下的實時數(shù)據(jù)交互提供了物理層支撐。例如,在光子計算芯片中,多芯MT-FA可實現(xiàn)激光器陣列與波導層的直接耦合,消除中間轉(zhuǎn)換環(huán)節(jié),使光信號傳輸效率提升40%以上。三維光子互連芯片的機械對準結(jié)構(gòu),通過V型槽實現(xiàn)光纖精確定位。西藏基于多芯MT-FA的三維光子互連系統(tǒng)

從工藝實現(xiàn)層面看,多芯MT-FA的制造涉及超精密加工、光學鍍膜、材料科學等多學科交叉技術(shù)。其重要工藝包括:采用五軸聯(lián)動金剛石車床對光纖陣列端面進行42.5°非球面研磨,表面粗糙度需控制在Ra<5nm;通過紫外固化膠水實現(xiàn)光纖與V槽的亞微米級定位,膠水收縮率需低于0.1%以避免應(yīng)力導致的偏移;端面鍍制AR/HR增透膜,使1550nm波段反射率低于0.1%。在可靠性測試中,該連接器需通過85℃/85%RH高溫高濕試驗、500次插拔循環(huán)測試以及-40℃至85℃溫度沖擊試驗,確保在數(shù)據(jù)中心24小時不間斷運行場景下的穩(wěn)定性。值得注意的是,多芯MT-FA的模塊化設(shè)計使其可兼容QSFP-DD、OSFP等主流光模塊接口標準,通過標準化插芯實現(xiàn)即插即用。隨著硅光集成技術(shù)的演進,未來多芯MT-FA將向更高密度發(fā)展,例如采用空芯光纖技術(shù)可將通道數(shù)擴展至72芯,同時通過3D打印技術(shù)實現(xiàn)定制化端面結(jié)構(gòu),進一步降低光子芯片的封裝復(fù)雜度。這種技術(shù)迭代不僅推動了光通信向1.6T及以上速率邁進,更為光子計算、量子通信等前沿領(lǐng)域提供了關(guān)鍵的基礎(chǔ)設(shè)施支撐。西藏基于多芯MT-FA的三維光子互連系統(tǒng)三維光子互連芯片在高速光通信領(lǐng)域具有巨大的應(yīng)用潛力。

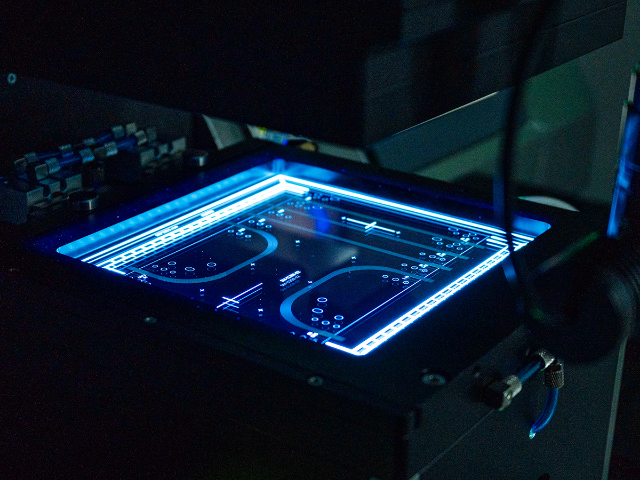

基于多芯MT-FA的三維光子互連標準正成為推動高速光通信技術(shù)革新的重要規(guī)范。該標準聚焦于多芯光纖陣列(Multi-FiberTerminationFiberArray,MT-FA)與三維光子集成技術(shù)的深度融合,通過精密的光子器件布局與三維光波導網(wǎng)絡(luò)設(shè)計,實現(xiàn)芯片間光信號的高效并行傳輸。多芯MT-FA作為關(guān)鍵組件,采用V形槽基板固定多根單模或多模光纖,通過42.5°端面研磨實現(xiàn)光信號的全反射耦合,結(jié)合低損耗MT插芯將通道間距控制在0.25mm以內(nèi),確保多路光信號在亞毫米級空間內(nèi)實現(xiàn)零串擾傳輸。其重要優(yōu)勢在于通過三維堆疊架構(gòu)突破傳統(tǒng)二維平面的密度限制,例如在800G光模塊中,80個光通信收發(fā)器可集成于0.3mm2芯片面積,單位面積數(shù)據(jù)密度達5.3Tb/s/mm2,較傳統(tǒng)方案提升一個數(shù)量級。該標準還定義了光子器件與電子芯片的垂直互連規(guī)范,通過銅錫熱壓鍵合技術(shù)形成15μm間距的2304個互連點,既保證114.9MPa的機械強度,又將電容降至10fF,實現(xiàn)低功耗、高可靠的片上光電子集成。

三維光子集成技術(shù)與多芯MT-FA光收發(fā)模塊的深度融合,正在重塑高速光通信系統(tǒng)的技術(shù)邊界。傳統(tǒng)光模塊受限于二維平面集成架構(gòu),其光子與電子組件的橫向排列導致通道密度受限、傳輸損耗累積,難以滿足800G/1.6T時代對低能耗、高帶寬的嚴苛需求。而三維集成通過垂直堆疊光子芯片與電子芯片,結(jié)合銅柱凸點高密度鍵合工藝,實現(xiàn)了光子發(fā)射器與接收器單元在0.15mm2面積內(nèi)的80通道密集排列。這種架構(gòu)突破了平面布局的物理限制,使單芯片光子通道數(shù)從早期64路提升至80路,同時將電光轉(zhuǎn)換能耗降低至120fJ/bit以下,較傳統(tǒng)方案降幅超過50%。多芯MT-FA組件作為三維架構(gòu)中的重要連接單元,其42.5°端面全反射設(shè)計與V槽pitch±0.5μm的精密加工,確保了多路光信號在垂直堆疊結(jié)構(gòu)中的低損耗傳輸。通過將光纖陣列與三維集成光子芯片直接耦合,MT-FA不僅簡化了光路對準工藝,更將模塊體積縮小40%,為數(shù)據(jù)中心高密度機柜部署提供了關(guān)鍵支撐。三維光子互連芯片的光子傳輸不受傳統(tǒng)金屬互連的帶寬限制,為數(shù)據(jù)傳輸速度的提升打開了新的空間。

多芯MT-FA光收發(fā)組件在三維光子集成體系中的創(chuàng)新應(yīng)用,正推動光通信向超高速、低功耗方向加速演進。針對1.6T光模塊的研發(fā)需求,三維集成技術(shù)通過波導總線架構(gòu)將80個通道組織為20組四波長并行傳輸單元,使單模塊帶寬密度提升至10Tbps/mm2。多芯MT-FA組件在此架構(gòu)中承擔雙重角色:其微米級V槽間距精度確保了多芯光纖與光子芯片的亞波長級對準,而保偏型FA設(shè)計則維持了相干光通信所需的偏振態(tài)穩(wěn)定性。在能效優(yōu)化方面,三維集成使MT-FA組件與硅基調(diào)制器、鍺光電二極管的電容耦合降低60%,配合垂直p-n結(jié)微盤諧振器的低電壓驅(qū)動特性,系統(tǒng)整體功耗較傳統(tǒng)方案下降45%。市場預(yù)測表明,隨著AI大模型參數(shù)規(guī)模突破萬億級,數(shù)據(jù)中心對1.6T光模塊的年需求量將在2027年突破千萬只,而具備三維集成能力的多芯MT-FA組件將占據(jù)高級市場60%以上份額。該技術(shù)路線不僅解決了高速光互聯(lián)的密度瓶頸,更為6G通信、量子計算等前沿領(lǐng)域提供了低延遲、高可靠的物理層支撐。三維光子互連芯片的氫氟酸蝕刻參數(shù)調(diào)控,優(yōu)化TGV深寬比。西藏基于多芯MT-FA的三維光子互連系統(tǒng)

邊緣計算設(shè)備升級,三維光子互連芯片推動終端數(shù)據(jù)處理能力大幅提升。西藏基于多芯MT-FA的三維光子互連系統(tǒng)

三維光子芯片多芯MT-FA光連接標準的制定,是光通信技術(shù)向高密度、低損耗方向演進的重要支撐。隨著數(shù)據(jù)中心單模塊速率從800G向1.6T跨越,傳統(tǒng)二維平面封裝已無法滿足硅光芯片與光纖陣列的耦合需求。三維結(jié)構(gòu)通過垂直堆疊技術(shù),將多芯MT-FA(Multi-FiberArray)的通道數(shù)從12芯提升至48芯甚至更高,同時利用硅基波導的立體折射特性,實現(xiàn)模場直徑(MFD)的精確匹配。例如,采用超高數(shù)值孔徑(UHNA)光纖與標準單模光纖的拼接工藝,可將模場從3.2μm轉(zhuǎn)換至9μm,插損控制在0.2dB以下。這種三維集成方案不僅縮小了光模塊體積,更通過V槽基板的亞微米級精度(±0.3μm公差),確保多芯并行傳輸時的通道均勻性,滿足AI算力集群對長時間高負載數(shù)據(jù)傳輸?shù)姆€(wěn)定性要求。此外,三維結(jié)構(gòu)還兼容共封裝光學(CPO)架構(gòu),通過將MT-FA直接嵌入光引擎內(nèi)部,減少外部連接損耗,為未來3.2T光模塊的研發(fā)奠定物理層基礎(chǔ)。西藏基于多芯MT-FA的三維光子互連系統(tǒng)

- 廣州MT-FA多芯光纖連接器價格 2025-12-22

- 多芯光纖連接器SC/PC APC混合廠家直銷 2025-12-22

- 山西空芯光纖連接器的作用 2025-12-22

- 哈爾濱空芯光纖連接器標準 2025-12-21

- 成都多芯MT-FA光組件失效分析 2025-12-21

- 西寧數(shù)字化空芯光纖連接器 2025-12-21

- 新疆空芯光纖連接器有哪幾種 2025-12-21

- 拉薩空芯光纖 2025-12-21

- 鄭州多芯MT-FA光組件溫度穩(wěn)定性 2025-12-21

- 成都多芯MT-FA光組件在超算中的應(yīng)用 2025-12-21

- 荊州數(shù)智化采控一體屏解決方案 2025-12-22

- 浙江耐酸堿網(wǎng)線報價 2025-12-22

- 重慶智能高低壓開關(guān)柜原理圖 2025-12-22

- 廣州MT-FA多芯光纖連接器價格 2025-12-22

- 微呼寶外貿(mào)電話Skype 2025-12-22

- 金華哪些嵌入式開發(fā)客服電話 2025-12-22

- 國內(nèi)消費級定位模組報價單 2025-12-22

- 江西智能高低壓開關(guān)柜成套設(shè)備 2025-12-22

- 云南循環(huán)發(fā)卡酒店自助機廠家精選 2025-12-22

- 無錫如何光通信設(shè)備銷售 2025-12-22