遼寧IBE材料刻蝕服務

硅材料刻蝕技術是半導體制造領域的關鍵技術之一,近年來取得了卓著的進展。隨著納米技術的不斷發展,對硅材料刻蝕的精度和效率提出了更高的要求。為了滿足這些需求,人們不斷研發新的刻蝕方法和工藝。其中,ICP(感應耦合等離子)刻蝕技術以其高精度、高均勻性和高選擇比等優點而備受關注。通過優化ICP刻蝕工藝參數,如等離子體密度、刻蝕氣體成分和流量等,可以實現對硅材料表面形貌的精確控制。此外,隨著新型刻蝕氣體的開發和應用,如含氟氣體和含氯氣體等,進一步提高了硅材料刻蝕的效率和精度。這些比較新進展為半導體制造領域的發展提供了有力支持,推動了相關技術的不斷創新和進步。氮化鎵是一種具有優異的光電性能和高溫穩定性的寬禁帶半導體材料。遼寧IBE材料刻蝕服務

硅材料刻蝕是集成電路制造過程中的關鍵步驟之一,對于實現高性能、高集成度的電路結構具有重要意義。在集成電路制造中,硅材料刻蝕技術被普遍應用于制備晶體管、電容器等元件的溝道、電極等結構。這些結構的尺寸和形狀對器件的性能具有重要影響。通過精確控制刻蝕深度和寬度,可以優化器件的電氣性能,提高集成度和可靠性。此外,硅材料刻蝕技術還用于制備微小通道、精細圖案等復雜結構,為集成電路的微型化、集成化提供了有力支持。隨著半導體技術的不斷發展,硅材料刻蝕技術也在不斷創新和完善,如采用ICP刻蝕等新技術,進一步提高了刻蝕精度和加工效率,為集成電路的持續發展注入了新的活力。中山氮化鎵材料刻蝕服務價格深硅刻蝕設備在生物醫學領域也有著重要的應用,主要用于制造生物芯片、微針、微梳等。

放電參數包括放電功率、放電頻率、放電壓力、放電時間等,它們直接影響著等離子體的密度、能量、溫度。放電頻率越高,等離子體能量越低,刻蝕方向性越好;放電壓力越低,等離子體平均自由程越長,刻蝕方向性越好;放電時間越長,刻蝕深度越大,但也可能造成刻蝕副反應和表面損傷。半導體介質層是指在半導體器件中用于隔離、絕緣、保護或調節電場的非導電材料層,如氧化硅、氮化硅、氧化鋁等。這些材料具有較高的介電常數和較低的損耗,對半導體器件的性能和可靠性有重要影響。為了制備高性能的半導體器件,需要對半導體介質層進行精密的刻蝕處理,形成所需的結構和圖案。刻蝕是一種通過物理或化學手段去除材料表面或內部的一部分,以改變其形狀或性質的過程。刻蝕可以分為濕法刻蝕和干法刻蝕兩種。濕法刻蝕是指將材料浸入刻蝕液中,利用液體與固體之間的化學反應來去除材料的一種方法。干法刻蝕是指利用高能粒子束(如離子束、等離子體、激光等)與固體之間的物理或化學作用來去除材料的一種方法。

材料刻蝕技術是半導體產業中的中心技術之一,對于實現高性能、高集成度的半導體器件具有重要意義。隨著半導體技術的不斷發展,材料刻蝕技術也在不斷創新和完善。從早期的濕法刻蝕到現在的干法刻蝕(如ICP刻蝕),每一次技術革新都推動了半導體產業的快速發展。材料刻蝕技術不只決定了半導體器件的尺寸和形狀,還直接影響其電氣性能、可靠性和成本。因此,材料刻蝕技術的研發和創新對于半導體產業的持續發展和競爭力提升具有戰略地位。未來,隨著新材料、新工藝的不斷涌現,材料刻蝕技術將繼續向更高精度、更復雜結構的加工方向發展,為半導體產業的持續創新和應用拓展提供有力支撐。深硅刻蝕設備的原理是基于博世過程或低溫過程,利用氟化物等離子體對硅進行刻蝕。

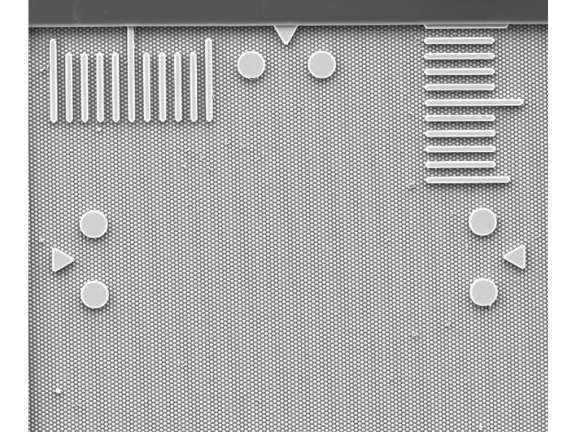

MEMS慣性傳感器領域依賴離子束刻蝕實現性能突破,其創新的深寬比控制技術解決高精度陀螺儀制造的痛點。通過建立雙離子源協同作用機制,在硅基底加工出深寬比超過25:1的微柱陣列結構。該工藝的重心突破在于發展出智能終端檢測系統與自補償算法,使諧振結構的熱漂移系數降至十億分之一級別,為自動駕駛系統提供超越衛星精度的慣性導航模塊。中性束刻蝕技術開啟介電材料加工新紀元,其獨特的粒子中性化機制徹底解決柵氧化層電荷損傷問題。在3nm邏輯芯片制造中,該技術創造性地保持原子級柵極界面完整性,使電子遷移率提升兩倍。主要技術突破在于發展出能量分散控制模塊,在納米鰭片加工中完美維持介電材料的晶體結構,為集成電路微縮提供原子級無損加工工藝路線。Bosch工藝作為深硅刻蝕的基本工藝,采用SF6和C4F8循環刻蝕實現高深寬比的硅刻蝕。天津IBE材料刻蝕廠家

深硅刻蝕設備在這些光學開關中主要用于形成微鏡陣列、液晶單元等。遼寧IBE材料刻蝕服務

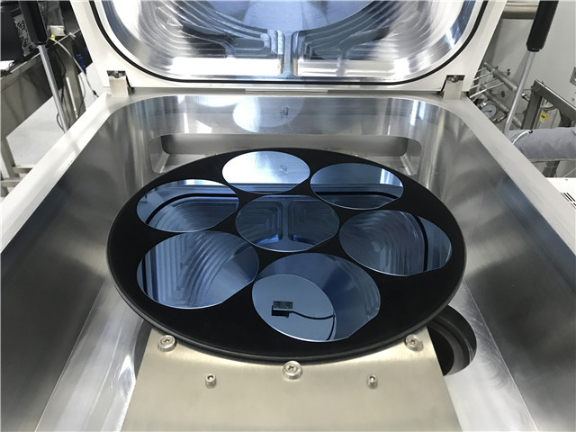

TSV制程的主要工藝流程包括以下幾個步驟:?深反應離子刻蝕(DRIE)法形成通孔,通孔的直徑、深度、形狀和位置都需要精確控制;?化學氣相沉積(CVD)法沉積絕緣層,絕緣層的厚度、均勻性和質量都需要滿足要求;?物理的氣相沉積(PVD)法沉積阻擋層和種子層,阻擋層和種子層的連續性、覆蓋率和粘合強度都需要保證;?電鍍法填充銅,銅填充的均勻性、完整性和缺陷都需要檢測;?化學機械拋光(CMP)法去除多余的銅,使表面平整;?晶圓減薄和鍵合,將含有TSV的晶圓與其他晶圓或基板進行垂直堆疊。遼寧IBE材料刻蝕服務

- 河北陽極晶圓鍵合加工 2025-12-22

- 云南高溫晶圓鍵合加工 2025-12-22

- 廣州硅熔融晶圓鍵合廠商 2025-12-22

- 吉林玻璃焊料晶圓鍵合代工 2025-12-22

- 生物探針電子束曝光廠商 2025-12-22

- 北京量子器件電子束曝光加工廠商 2025-12-22

- 安徽光掩模電子束曝光技術 2025-12-20

- 佛山量子器件電子束曝光加工廠 2025-12-20

- 東莞精密晶圓鍵合服務價格 2025-12-20

- 北京高溫晶圓鍵合代工 2025-12-20

- 內蒙古簡牛線束 2025-12-22

- 廣州地下停車場車牌識別屏設計 2025-12-22

- 成都電阻式壓力分布檢測 2025-12-22

- 惠州旋轉式金屬柄編碼器購買 2025-12-22

- 廈門哪里有工業控制板卡設計 2025-12-22

- 清遠行業經驗傳統骨架成型方案 2025-12-22

- 福建萬兆光模塊 2025-12-22

- 鹽城非標自動化數控系統定制 2025-12-22

- 佛山半導體放電管參數詳解 2025-12-22

- 綿陽威視智能車牌識別屏 2025-12-22