深圳半導體材料刻蝕外協

干法刻蝕設備是一種利用等離子體產生的高能離子和自由基,與被刻蝕材料發生物理碰撞和化學反應,從而去除材料并形成所需特征的設備。干法刻蝕設備是半導體制造工藝中不可或缺的一種設備,它可以實現高縱橫比、高方向性、高精度、高均勻性、高重復性等性能,以滿足集成電路的不斷微型化和集成化的需求。干法刻蝕設備的制程主要包括以下幾個步驟:一是樣品加載,即將待刻蝕的樣品放置在設備中的電極上,并固定好;二是氣體供應,即根據不同的工藝需求,向反應室內輸送不同種類和比例的氣體,并控制好氣體流量和壓力;三是等離子體激發,即通過不同類型的電源系統,向反應室內施加電場或磁場,從而激發出等離子體;四是刻蝕過程,即通過控制等離子體的密度、溫度、能量等參數,使等離子體中的活性粒子與樣品表面發生物理碰撞和化學反應,從而去除材料并形成特征;五是終點檢測,即通過不同類型的檢測系統,監測樣品表面的反射光強度、電容變化、質譜信號等指標,從而確定刻蝕是否達到預期的結果;六是樣品卸載,即將刻蝕完成的樣品從設備中取出,并進行后續的清洗、檢測和封裝等工藝。刻蝕是用化學或物理方法有選擇地從硅片表面去除不需要的材料的過程,主要對各種薄膜以及體硅進行加工。深圳半導體材料刻蝕外協

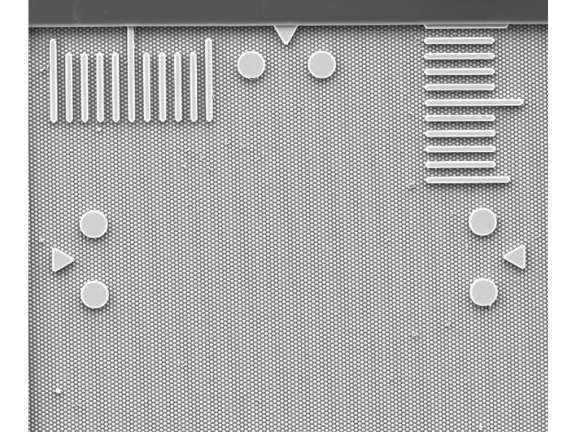

現代離子束刻蝕裝備融合等離子體物理與精密工程技術,其多極磁場約束系統實現束流精度質的飛躍。在300mm晶圓量產中,創新七柵離子光學結構與自適應控制算法完美配合,將刻蝕均勻性推至亞納米級別。突破性突破在于發展出晶圓溫度實時補償系統,消除熱形變導致的圖形畸變,支撐半導體制造進入原子精度時代。離子束刻蝕在高級光學制造領域開創非接觸加工新范式,其納米級選擇性去除技術實現亞埃級面形精度。在極紫外光刻物鏡制造中,該技術成功應用駐留時間控制算法,將300mm非球面鏡的面形誤差控制在0.1nm以下。突破性在于建立大氣環境與真空環境的精度轉換模型,使光學系統波像差達到0.5nm極限,支撐3nm芯片制造的光學系統量產。福州刻蝕設備深硅刻蝕設備在半導體領域有著重要的應用,主要用于制造先進存儲器、邏輯器件、射頻器件、功率器件等。

。ICP類型具有較高的刻蝕速率和均勻性,但由于離子束和自由基的比例難以控制,導致刻蝕的方向性和選擇性較差,以及扇形效應較大等缺點;三是磁控增強反應離子刻蝕(MERIE),該類型是指在RIE類型的基礎上,利用磁場增強等離子體的密度和均勻性,從而提高刻蝕速率和均勻性,同時降低離子束的能量和方向性,從而減少物理損傷和加熱效應,以及改善刻蝕的方向性和選擇性。MERIE類型具有較高的刻蝕速率、均勻性、方向性和選擇性,但由于磁場的存在,導致設備的結構和控制較為復雜,以及磁場對樣品表面造成的影響難以預測等缺點。

深硅刻蝕設備在微機電系統(MEMS)領域也有著重要的應用,主要用于制造傳感器、執行器、微流體器件、光學開關等。其中,傳感器是指用于檢測物理量或化學量并將其轉換為電信號的器件,如加速度傳感器、壓力傳感器、溫度傳感器、濕度傳感器等。深硅刻蝕設備在這些傳感器中主要用于形成懸臂梁、橋式結構、薄膜結構等。執行器是指用于接收電信號并將其轉換為物理運動或化學反應的器件,如微鏡片、微噴嘴、微泵等。深硅刻蝕設備在這些執行器中主要用于形成可動部件、驅動機構、密封結構等。Bosch工藝作為深硅刻蝕的基本工藝,采用SF6和C4F8循環刻蝕實現高深寬比的硅刻蝕。

深硅刻蝕設備在半導體領域有著重要的應用,主要用于制作通孔硅(TSV)。TSV是一種垂直穿過芯片或晶圓的結構,可以實現芯片或晶圓之間的電氣連接,是一種先進的封裝技術,可以提高芯片或晶圓的集成度、性能和可靠性。TSV的制作需要使用深硅刻蝕設備,在芯片或晶圓上開出深度和高方面比的孔,并在孔壁上沉積絕緣層和導電層,形成TSV結構。TSV結構對深硅刻蝕設備提出了較高的要求。低溫過程采用較低的溫度(約-100攝氏度)和較長的循環時間(約幾十秒),形成較小的刻蝕速率和較平滑的壁紋理,適用于制作小尺寸和低深寬比的結構二氧化硅的濕法刻蝕可以使用氫氟酸(HF)作為刻蝕劑,通常在刻蝕溶液中加入氟化銨作為緩沖劑。化學刻蝕

離子束刻蝕是超導量子比特器件實現原子級界面加工的主要技術。深圳半導體材料刻蝕外協

氧化鎵刻蝕制程是一種在半導體制造中用于形成氧化鎵(Ga2O3)結構的技術,它具有以下幾個特點:?氧化鎵是一種具有高帶隙(4.8eV)、高擊穿電場(8MV/cm)、高熱導率(25W/mK)等優異物理性能的材料,適合用于制作高功率、高頻率、高溫、高效率的電子器件;氧化鎵可以通過水熱法、分子束外延法、金屬有機化學氣相沉積法等方法在不同的襯底上生長,形成單晶或多晶薄膜;氧化鎵的刻蝕制程主要采用干法刻蝕,即利用等離子體或離子束對氧化鎵進行物理轟擊或化學反應,將氧化鎵去除,形成所需的圖案;氧化鎵的刻蝕制程需要考慮以下幾個因素:刻蝕速率、選擇性、均勻性、側壁傾斜度、表面粗糙度、缺陷密度等,以保證刻蝕的質量和精度。深圳半導體材料刻蝕外協

- 山東NEMS器件電子束曝光服務 2025-12-16

- 安徽光芯片電子束曝光工藝 2025-12-16

- 河北圖形化電子束曝光工藝 2025-12-16

- 深圳高溫晶圓鍵合代工 2025-12-16

- 安徽AR/VR電子束曝光加工平臺 2025-12-16

- 珠海陽極晶圓鍵合外協 2025-12-16

- 貴州高分辨電子束曝光技術 2025-12-16

- 安徽圖形化電子束曝光服務 2025-12-16

- 佛山光芯片電子束曝光實驗室 2025-12-16

- 吉林高溫晶圓鍵合價錢 2025-12-15

- 江門醫療線路板雙層板 2025-12-16

- 湖南有什么穩壓二極管行業 2025-12-16

- 北京atc高Q值電容 2025-12-16

- 惠山區電子元器件型號 2025-12-16

- 中國臺灣激光器參考價格 2025-12-16

- NX5032GA 40.63125MHZ晶振 2025-12-16

- 江蘇質量可控硅模塊推薦廠家 2025-12-16

- 四川交流晶閘管調壓模塊型號 2025-12-16

- 湖南氫化釜用氧氣分析儀排行榜 2025-12-16

- 怎么用鉆具量具治具工具生產設備用射頻識別盤點市價 2025-12-16