遼寧ZYNQFPGA開發板

FPGA開發板的信號完整性是指信號在傳輸過程中保持原有特性的能力,直接影響系統的穩定性和性能,尤其在高速接口(如PCIe、DDR、HDMI)設計中至關重要。信號完整性優化需從PCB設計、元器件選型和時序約束三個方面入手。PCB設計中,需控制傳輸線阻抗匹配(如50Ω、100Ω差分),避免阻抗突變導致信號反射;采用差分信號傳輸,減少電磁干擾(EMI);優化布線拓撲,縮短信號路徑,減少串擾。元器件選型中,需選用高速率、低抖動的晶體振蕩器和時鐘緩沖器,確保時鐘信號穩定;選用低寄生參數的連接器和電容電阻,減少信號衰減。時序約束中,需在開發工具中設置合理的時鐘周期、建立時間和保持時間,確保數據在正確的時序窗口內傳輸;通過時序分析工具檢查時序違規,調整邏輯布局和布線,實現時序收斂。信號完整性問題常表現為數據傳輸錯誤、圖像失真、接口不穩定,可通過示波器觀察信號波形,分析反射、串擾、抖動等問題,針對性優化設計。 FPGA 開發板示例代碼注釋清晰便于學習。遼寧ZYNQFPGA開發板

FPGA開發板的擴展模塊兼容性可提升系統靈活性,常見的擴展接口包括PMOD接口、Arduino接口、HAT接口等,支持連接各類功能模塊。PMOD接口是Digilent推出的標準接口,通常為6針或12針連接器,支持SPI、I2C、UART等通信協議,可連接傳感器模塊(如溫濕度傳感器、加速度傳感器)、通信模塊(如WiFi模塊、藍牙模塊)、顯示模塊(如OLED模塊、LCD模塊)。Arduino接口兼容ArduinoUno的引腳定義,可直接使用Arduino生態的擴展模塊,如電機驅動模塊、繼電器模塊,方便開發者復用現有資源。HAT接口是樹莓派推出的擴展接口,部分FPGA開發板支持HAT接口,可與樹莓派協同工作,實現“FPGA+MCU”的異構計算架構,例如樹莓派負責上層應用開發,FPGA負責底層硬件加速。擴展模塊兼容性需考慮接口電平匹配和時序兼容性,部分開發板會提供擴展模塊的接線指南和示例代碼,簡化模塊集成過程,幫助開發者快速搭建系統。 浙江安路FPGA開發板學習步驟FPGA 開發板電源管理支持多種供電方式。

數碼管是FPGA開發板上用于數字顯示的外設,分為共陰極和共陽極兩種類型,通常以4位或8位組合形式存在,可顯示0-9的數字和部分字母。其工作原理是通過FPGA輸出的段選信號(控制顯示的數字或字母)和位選信號(控制點亮的數碼管),實現動態掃描顯示。在數字計數、時鐘設計等項目中,數碼管可直觀顯示數值信息,例如顯示計數器的當前數值、定時器的剩余時間。部分開發板會集成數碼管驅動芯片,將FPGA的并行控制信號轉換為數碼管所需的驅動信號,減少FPGA引腳占用;也有開發板直接通過FPGA引腳驅動數碼管,適合教學場景,幫助學生理解動態掃描顯示的原理。在顯示控制中,需注意掃描頻率的設置,通常需高于50Hz以避免肉眼觀察到閃爍現象,提升顯示效果。

FPGA開發板的功耗管理是開發者需要關注的重要方面。在便攜式設備或電池供電的應用場景中,降低開發板功耗尤為關鍵。開發者可通過優化FPGA邏輯設計,減少不必要的邏輯翻轉,降低芯片動態功耗。合理配置開發板外設,在不使用時將其設置為低功耗模式,進一步降低系統功耗。部分開發板提供專門的功耗管理模塊,幫助開發者監控與調節功耗,通過軟件設置實現不同的功耗管理策略。良好的功耗管理使FPGA開發板能夠在低功耗狀態下穩定運行,滿足特定應用場景對功耗的嚴格要求,延長設備續航時間。FPGA 開發板是否支持遠程調試功能?

科研人員在進行前沿技術研究時,FPGA開發板是重要的工具之一。在人工智能領域,科研人員利用開發板實現神經網絡算法的硬件加速,通過編程優化神經網絡計算過程,提高計算效率。在生物醫學工程(不涉及醫療內容)領域外的相關研究中,如生物傳感器信號處理研究,開發板可用于處理生物電信號,分析信號特征。FPGA開發板的靈活性與可編程性,使科研人員能夠快速實現新的研究思路與算法,對采集的數據進行實時處理與分析,為各領域前沿技術研究提供實驗平臺,推動科研工作的進展與創新。FPGA 開發板是否提供過流保護功能?河南MPSOCFPGA開發板教學

FPGA 開發板按鍵消抖電路保證輸入穩定。遼寧ZYNQFPGA開發板

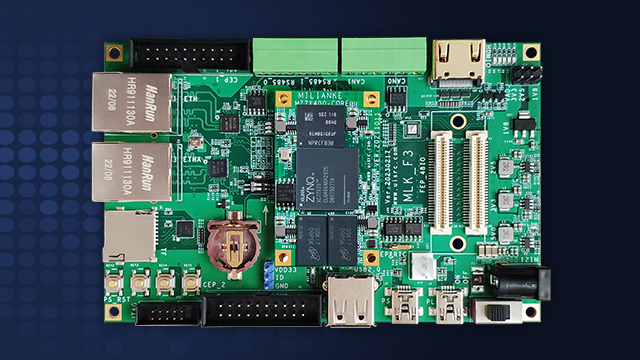

米聯客MIZ7010FPGA開發板(Zynq-7010款)面向低成本嵌入式項目開發,米聯客MIZ7010開發板選用XilinxZynq-7010芯片,集成雙核ARMCortex-A9處理器與28萬邏輯單元的FPGA資源,在控制成本的同時,保留軟硬件協同開發能力。硬件配置上,開發板搭載256MBDDR3內存、8GBeMMC閃存,板載USBOTG接口、UART串口、千兆以太網接口及2個40針擴展接口,可連接基礎外設,滿足輕量型嵌入式應用需求,如物聯網數據轉發、小型設備控制等。軟件支持方面,開發板提供簡化版Petalinux鏡像與Vitis開發工具,支持C語言與VerilogHDL混合編程,用戶可開發簡單的軟硬件協同應用。配套資料包含基礎Linux驅動開發案例、FPGA邏輯設計案例,如GPIO控制、以太網數據收發、SPI接口通信等,幫助用戶以較低成本掌握嵌入式開發技能。開發板尺寸為10cm×8cm,采用簡約設計,適合小型設備集成;同時具備過流保護功能,保障設備使用安全。該開發板可應用于低成本物聯網網關、小型工業控制器、教學實驗平臺等場景,為預算有限的項目提供高性價比解決方案。 遼寧ZYNQFPGA開發板

- 湖南XilinxFPGA開發板設計 2025-12-23

- 四川核心板FPGA開發板解決方案 2025-12-23

- 中國臺灣ZYNQFPGA開發板板卡設計 2025-12-23

- 中國臺灣XilinxFPGA開發板定制 2025-12-23

- 中國臺灣嵌入式FPGA開發板板卡設計 2025-12-23

- 遼寧賽靈思FPGA 2025-12-23

- 廣東開發板FPGA特點與應用 2025-12-23

- 江西入門級FPGA開發板語法 2025-12-23

- 遼寧賽靈思FPGA開發板交流 2025-12-23

- 北京ZYNQFPGA開發板平臺 2025-12-23

- 彩虹自動復位溫控器1688 2025-12-24

- 安徽工業制造薄膜壓力傳感器售后服務 2025-12-24

- 佛山聯芯橋UCB9436DC-DC升降壓轉換芯片原廠廠家 2025-12-24

- 成都YXC有源晶振廠家 2025-12-24

- 廣東55kw機電批發 2025-12-24

- 奉賢區智能電阻芯片批量定制 2025-12-24

- 梁溪區新型充電樁安裝供應商家 2025-12-24

- 四川RFID測溫雙頻標簽原料 2025-12-24

- 33uH一體成型電感廠家 2025-12-24

- 紹興防偽芯片哪家好 2025-12-24