-

重塑組織再生未來(lái):BIONOVA X 打造可變形生物醫(yī)學(xué)支架

-

ELVEFLOW賦能血氨檢測(cè),效率超傳統(tǒng)實(shí)驗(yàn)室10倍

-

人類微心臟模型助力精細(xì)醫(yī)療與藥物研發(fā)

-

CERO全自動(dòng)3D細(xì)胞培養(yǎng),**hiPSC心肌球培養(yǎng)難題

-

皮膚移植3D生物打印調(diào)控血管分支新路徑

-

3D生物打印tumor模型,改寫免疫tumor學(xué)研究格局

-

高效刻蝕 WSe?新方案!CIONE-LF 等離子體系統(tǒng)實(shí)操

-

等離子體處理 PDMS 效果不穩(wěn)定的原因

-

生物3D打印模型突破先天性心臟病***困境!

-

Accutrol重新定義管道數(shù)字化氣流監(jiān)測(cè)標(biāo)準(zhǔn)

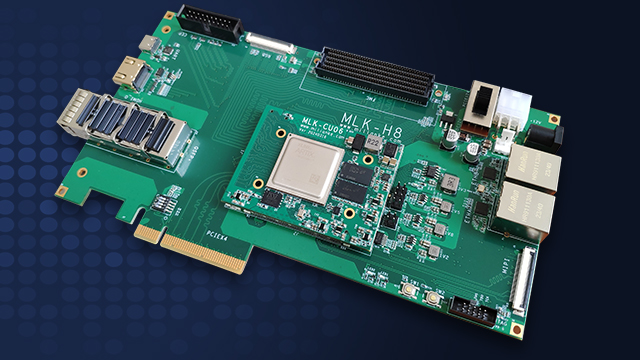

山東國(guó)產(chǎn)FPGA開發(fā)板入門

I2C接口是一種低成本、低速率的串行通信接口,在FPGA開發(fā)板中常用于連接EEPROM(電可擦除可編程只讀存儲(chǔ)器)、傳感器、實(shí)時(shí)時(shí)鐘(RTC)等外設(shè)。其典型架構(gòu)包括SDA(串行數(shù)據(jù)線)和SCL(串行時(shí)鐘線)兩根信號(hào)線,支持多主多從拓?fù)浣Y(jié)構(gòu),通過(guò)從機(jī)地址區(qū)分不同外設(shè)。在EEPROM應(yīng)用中,F(xiàn)PGA可通過(guò)I2C接口讀取或?qū)懭肱渲眯畔ⅲ绨蹇ㄐ蛄刑?hào)、硬件版本號(hào);在傳感器應(yīng)用中,可通過(guò)I2C接口讀取溫濕度傳感器、光照傳感器的數(shù)據(jù),實(shí)現(xiàn)環(huán)境監(jiān)測(cè);在RTC應(yīng)用中,可通過(guò)I2C接口獲取實(shí)時(shí)時(shí)間,為系統(tǒng)提供時(shí)間戳。I2C接口的傳輸速率較低,通常為100kbps(標(biāo)準(zhǔn)模式)或400kbps(快速模式),適合對(duì)傳輸速率要求不高的場(chǎng)景,但布線簡(jiǎn)單,只需兩根信號(hào)線,可減少PCB空間占用。部分FPGA開發(fā)板會(huì)集成I2C總線仲裁電路,支持多主機(jī)同時(shí)訪問(wèn)總線。 FPGA 開發(fā)板 USB 轉(zhuǎn)串口實(shí)現(xiàn)數(shù)據(jù)通信。山東國(guó)產(chǎn)FPGA開發(fā)板入門

FPGA開發(fā)板是電子工程師與愛(ài)好者探索硬件世界的重要載體,其硬件架構(gòu)設(shè)計(jì)精巧且功能豐富。以常見的XilinxZynq系列開發(fā)板為例,這類開發(fā)板集成了ARM處理器與FPGA可編程邏輯資源,形成獨(dú)特的異構(gòu)架構(gòu)。ARM處理器部分可運(yùn)行嵌入式操作系統(tǒng),用于處理復(fù)雜的系統(tǒng)管理任務(wù)和軟件算法,諸如文件系統(tǒng)管理、網(wǎng)絡(luò)通信協(xié)議棧運(yùn)行等;而FPGA部分則可根據(jù)設(shè)計(jì)需求靈活構(gòu)建各類數(shù)字電路。開發(fā)板上還配備了豐富的存儲(chǔ)模塊,包括用于程序存儲(chǔ)的Flash芯片,能在斷電后長(zhǎng)久保存系統(tǒng)啟動(dòng)代碼與用戶程序;以及用于數(shù)據(jù)緩存的DDR內(nèi)存,可在運(yùn)行時(shí)存取大量數(shù)據(jù)。此外,開發(fā)板設(shè)置多種通信接口,以太網(wǎng)接口方便連接網(wǎng)絡(luò)進(jìn)行數(shù)據(jù)傳輸與遠(yuǎn)程調(diào)試,USB接口支持多種設(shè)備連接,方便數(shù)據(jù)交互,SPI、I2C等接口則用于連接各類傳感器與外設(shè)芯片,為開發(fā)者搭建復(fù)雜硬件系統(tǒng)提供了充足的拓展空間。山東國(guó)產(chǎn)FPGA開發(fā)板入門FPGA 開發(fā)板配套仿真工具驗(yàn)證邏輯正確性。

FPGA開發(fā)板的教學(xué)實(shí)驗(yàn)案例設(shè)計(jì)需遵循由淺入深、理論與實(shí)踐結(jié)合的原則,覆蓋基礎(chǔ)邏輯、接口通信、綜合系統(tǒng)等層面,幫助學(xué)生逐步掌握FPGA設(shè)計(jì)技能。基礎(chǔ)邏輯實(shí)驗(yàn)包括邏輯門實(shí)現(xiàn)、觸發(fā)器應(yīng)用、計(jì)數(shù)器設(shè)計(jì)、狀態(tài)機(jī)設(shè)計(jì),例如“基于FPGA的4位計(jì)數(shù)器設(shè)計(jì)”實(shí)驗(yàn),學(xué)生通過(guò)編寫Verilog代碼實(shí)現(xiàn)計(jì)數(shù)器功能,通過(guò)LED觀察計(jì)數(shù)結(jié)果,理解時(shí)序邏輯的工作原理。接口通信實(shí)驗(yàn)包括UART通信、SPI通信、I2C通信、HDMI顯示,例如“基于FPGA的UART串口通信實(shí)驗(yàn)”,學(xué)生實(shí)現(xiàn)UART發(fā)送和接收模塊,通過(guò)串口助手與計(jì)算機(jī)通信,掌握串行通信協(xié)議。綜合系統(tǒng)實(shí)驗(yàn)包括數(shù)字時(shí)鐘、交通燈控制器、簡(jiǎn)易計(jì)算器、圖像采集顯示系統(tǒng),例如“基于FPGA的數(shù)字時(shí)鐘設(shè)計(jì)”實(shí)驗(yàn),學(xué)生整合計(jì)數(shù)器、數(shù)碼管顯示、按鍵控制模塊,實(shí)現(xiàn)時(shí)鐘的時(shí)、分、秒顯示和時(shí)間調(diào)整功能,培養(yǎng)系統(tǒng)設(shè)計(jì)能力。實(shí)驗(yàn)案例需配套詳細(xì)的實(shí)驗(yàn)指導(dǎo)書,包括實(shí)驗(yàn)?zāi)康摹⒃怼⒉襟E、代碼示例和思考題,部分案例還可提供仿真文件和測(cè)試向量,幫助學(xué)生驗(yàn)證設(shè)計(jì)正確性。

FPGA開發(fā)板的功耗分為靜態(tài)功耗和動(dòng)態(tài)功耗,靜態(tài)功耗是芯片未工作時(shí)的漏電流功耗,動(dòng)態(tài)功耗是芯片工作時(shí)邏輯切換和信號(hào)傳輸產(chǎn)生的功耗,選型和設(shè)計(jì)時(shí)需根據(jù)應(yīng)用場(chǎng)景優(yōu)化功耗。低功耗FPGA開發(fā)板通常采用40nm、28nm等先進(jìn)工藝芯片,集成功耗管理模塊,支持動(dòng)態(tài)電壓頻率調(diào)節(jié)(DVFS),可根據(jù)工作負(fù)載調(diào)整電壓和頻率,降低空閑時(shí)的功耗,適合便攜設(shè)備、物聯(lián)網(wǎng)節(jié)點(diǎn)等電池供電場(chǎng)景。例如XilinxZynqUltraScale+MPSoC系列芯片,支持多種功耗模式,靜態(tài)功耗可低至幾十毫瓦。高功耗開發(fā)板則注重性能,采用16nm、7nm工藝芯片,支持高速接口和大量并行計(jì)算,適合固定設(shè)備、數(shù)據(jù)中心等有穩(wěn)定電源供應(yīng)的場(chǎng)景。功耗優(yōu)化還可通過(guò)設(shè)計(jì)層面實(shí)現(xiàn),如減少不必要的邏輯切換、優(yōu)化時(shí)鐘網(wǎng)絡(luò)、使用低功耗IP核等。在實(shí)際應(yīng)用中,需平衡功耗與性能,例如邊緣計(jì)算場(chǎng)景需優(yōu)先考慮低功耗,而數(shù)據(jù)中心加速場(chǎng)景需優(yōu)先考慮性能。 FPGA 開發(fā)板讓理論知識(shí)轉(zhuǎn)化為實(shí)踐能力!

米聯(lián)客MIZ7010FPGA開發(fā)板(Zynq-7010款)面向低成本嵌入式項(xiàng)目開發(fā),米聯(lián)客MIZ7010開發(fā)板選用XilinxZynq-7010芯片,集成雙核ARMCortex-A9處理器與28萬(wàn)邏輯單元的FPGA資源,在控制成本的同時(shí),保留軟硬件協(xié)同開發(fā)能力。硬件配置上,開發(fā)板搭載256MBDDR3內(nèi)存、8GBeMMC閃存,板載USBOTG接口、UART串口、千兆以太網(wǎng)接口及2個(gè)40針擴(kuò)展接口,可連接基礎(chǔ)外設(shè),滿足輕量型嵌入式應(yīng)用需求,如物聯(lián)網(wǎng)數(shù)據(jù)轉(zhuǎn)發(fā)、小型設(shè)備控制等。軟件支持方面,開發(fā)板提供簡(jiǎn)化版Petalinux鏡像與Vitis開發(fā)工具,支持C語(yǔ)言與VerilogHDL混合編程,用戶可開發(fā)簡(jiǎn)單的軟硬件協(xié)同應(yīng)用。配套資料包含基礎(chǔ)Linux驅(qū)動(dòng)開發(fā)案例、FPGA邏輯設(shè)計(jì)案例,如GPIO控制、以太網(wǎng)數(shù)據(jù)收發(fā)、SPI接口通信等,幫助用戶以較低成本掌握嵌入式開發(fā)技能。開發(fā)板尺寸為10cm×8cm,采用簡(jiǎn)約設(shè)計(jì),適合小型設(shè)備集成;同時(shí)具備過(guò)流保護(hù)功能,保障設(shè)備使用安全。該開發(fā)板可應(yīng)用于低成本物聯(lián)網(wǎng)網(wǎng)關(guān)、小型工業(yè)控制器、教學(xué)實(shí)驗(yàn)平臺(tái)等場(chǎng)景,為預(yù)算有限的項(xiàng)目提供高性價(jià)比解決方案。 FPGA 開發(fā)板外設(shè)接口過(guò)壓保護(hù)保障安全。山東國(guó)產(chǎn)FPGA開發(fā)板入門

FPGA 開發(fā)板網(wǎng)絡(luò)接口支持遠(yuǎn)程調(diào)試。山東國(guó)產(chǎn)FPGA開發(fā)板入門

FPGA開發(fā)板在教育領(lǐng)域扮演著越來(lái)越重要的角色,成為數(shù)字電路和嵌入式系統(tǒng)教學(xué)的重要工具。通過(guò)FPGA開發(fā)板,學(xué)生和學(xué)習(xí)者可以實(shí)踐性地理解數(shù)字邏輯設(shè)計(jì)的原理,掌握HDL編程的技巧,并加深對(duì)現(xiàn)代電子系統(tǒng)的理解。許多高校和培訓(xùn)機(jī)構(gòu)已經(jīng)將FPGA開發(fā)板納入課程體系,幫助學(xué)生提升實(shí)際操作能力和創(chuàng)新能力。此外,F(xiàn)PGA開發(fā)板的豐富資源和開源社區(qū)也為學(xué)習(xí)者提供了大量的教程和項(xiàng)目實(shí)例,進(jìn)一步降低了學(xué)習(xí)門檻,促進(jìn)了電子工程專業(yè)人才的培養(yǎng)。山東國(guó)產(chǎn)FPGA開發(fā)板入門

- 使用FPGA開發(fā)板平臺(tái) 2025-12-15

- 上海開發(fā)板FPGA 2025-12-15

- 安徽學(xué)習(xí)FPGA定制 2025-12-14

- 河南專注FPGA加速卡 2025-12-14

- 重慶專注FPGA開發(fā)板 2025-12-14

- 安徽Z(yǔ)YNQFPGA平臺(tái) 2025-12-14

- 湖北安路FPGA代碼 2025-12-14

- 江西安路FPGA基礎(chǔ) 2025-12-14

- 山東國(guó)產(chǎn)FPGA開發(fā)板入門 2025-12-14

- 山西賽靈思FPGA論壇 2025-12-14

- 國(guó)產(chǎn)激光器技術(shù)規(guī)范 2025-12-15

- 汕頭微源LP6222DC-DC升降壓轉(zhuǎn)換芯片半導(dǎo)體元器件 2025-12-15

- 連云港不銹鋼扣重載連接器聯(lián)系方式 2025-12-15

- 上海核心板價(jià)格 2025-12-15

- 深圳石英晶體振蕩器哪家好 2025-12-15

- 杭州快速電路板抄板報(bào)價(jià) 2025-12-15

- 天津手機(jī)FPC貼片供貨商 2025-12-15

- 金華拉桿式注塑機(jī)電子尺位移 2025-12-15

- 代理整流二極管有哪些 2025-12-15

- 吉林ESP32-C6-MINI-1價(jià)格表 2025-12-15